Contains the information about the registers used for the clocks. More...

#include <hardware.hpp>

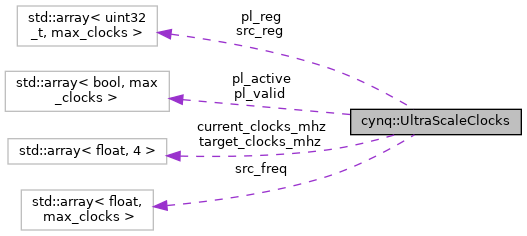

Data Fields | |

| std::array< bool, max_clocks > | pl_active = {false} |

| std::array< bool, max_clocks > | pl_valid = {false} |

| std::array< float, max_clocks > | src_freq = {0.f} |

| std::array< uint32_t, max_clocks > | pl_reg |

| std::array< uint32_t, max_clocks > | src_reg |

| std::array< float, 4 > | target_clocks_mhz = {-1.f} |

| std::array< float, 4 > | current_clocks_mhz = {-1.f} |

Static Public Attributes | |

| static constexpr int | max_clocks = 4 |

Contains the information about the registers used for the clocks.

| std::array<float, 4> cynq::UltraScaleClocks::current_clocks_mhz = {-1.f} |

Current clocks: used in UltraScale+

| std::array<bool, max_clocks> cynq::UltraScaleClocks::pl_active = {false} |

Verifies if the PL clock is enabled

| std::array<uint32_t, max_clocks> cynq::UltraScaleClocks::pl_reg |

Contains the information about the queried pl registers

| std::array<bool, max_clocks> cynq::UltraScaleClocks::pl_valid = {false} |

Verifies if the PL clock is valid

| std::array<float, max_clocks> cynq::UltraScaleClocks::src_freq = {0.f} |

Contains the source clock frequency

| std::array<uint32_t, max_clocks> cynq::UltraScaleClocks::src_reg |

Contains the information about the queried source registers

| std::array<float, 4> cynq::UltraScaleClocks::target_clocks_mhz = {-1.f} |

Target clocks: used in UltraScale+